Внешняя шина — данные

Внешняя шина данных выходит за пределы МП. Эти шины обеспечивают пропуск кодовой комбинации ( слова) на число разрядов, на которое рассчитан данный МП. У наиболее распространенных однокристальных МП ширина шины данных или магистрали составляет восемь разрядов. Связь внутри МП и с внешними устройствами осуществляется также с помощью шины адреса и шины управления.

Микросхемы представляют собой 16-битовый микропроцессор с 8-битовой внешней шиной данных ( центральное процессорное устройство с байтовым принципом организации) и предназначены для перевода аппаратных средств, построенных на К580ВМ80 и К580ВМ85, на программную среду К1810ВМ86 для повышения производительности. Различия состоят в изменении разрядности шины данных и соответствующих изменениях структуры и работы шинного интерфейса. БНЕзаме-нена линией состояния SSO, так как К1810ВМ88 может обращаться только к байтам и надобность в сигнале разрешения старшего байта шины SHE отпадает.

Как и процессор 8086, 80286 имеет 16-разрядную внешнюю шину данных и 6-байтный конвейер команд. Однако быстродействие процессора 80286 при тактовой частоте 12 5 МГц примерно в 6 раз выше, чем у 8086 с тактовой частотой 5 М Гц. Это достигается за счет усовершенствованной архитектуры и снижения количества тактов на одну команду.

Интегральная схема KJ810BM88 представляет собой 16-битовый микропроцессор с 8-битовой внешней шиной данных. Он предназначен прежде всего для перевода аппаратных средств, построенных на базе МП К580ВМ80 и К580ВМ85, на программную среду МП К1810ВМ86 с целью повышения производительности этих средств. Микропроцессоры ВМ86 и ВМ88 имеют аналогичную архитектуру и одинаковую систему команд. В ВМ88 сохранены 16-битовые общие и сегментные регистры, АЛУ для обработки 16-битовых операндов, сумматор для вычисления 20-битового физического адреса и средства поддержки многопроцессорных систем. Различия между этими двумя МП состоят в изменении разрядности шины данных и соответствующих изменениях структуры и работы шинного интерфейса.

|

Принцип двунаправленной, rj днных и алпеоа поелостав-передачи между внутренней и внеш — шин Данных и адреса., предосгав ней шинами данных ляя их в распоряжение внешних. |

Буферы данных и буферы адреса обеспечивают связь центрального процессора с внешними шинами данных и адреса. Особенность буферов состоит в том, что в каждом разряде они используют логические элементы с тремя состо-яниями.

Промежуточное положение между 8-разрядными и обычными 16-разрядными занимают 16-разрядные МП с 8-разрядной внешней шиной данных. Они представляют собой специальные модификации обычных 16-разрядных МП и обладают практически той же вычислительной мощностью, но в них используются более дешевые аппаратные схемы управления шиной.

Обмен 8-разрядными командами и данными между микропроцессором и внешними устройствами производится по 8-разрядной внешней шине данных DO — D7 через буферный регистр данных, который может находиться в трех состояниях — О, 1 и с высоким выходным сопротивлением, т.е. когда он отключается от внешней шины данных.

|

Структурная схема однокристального МП. |

Буферный регистр данных используется для временного хранения выбранного из памяти слова перед выдачей его во внешнюю шину данных. Его разрядность определяется количеством байтов информационного слова.

|

Типовая структура цифровой системы обработки сигналов. |

Как показано в табл. 2.5, в 1986 г. были выпущено много новых ПЦОС-СБИС; некоторые из них снабжены 32-разрядными внешними шинами данных, а в некоторых предусмотрена возможность арифметической обработки с плавающей запятой. Хорошим показателем производительности ПЦОС-СБИС является время выполнения 1024-точечного комплексного быстрого преобразования Фурье ( БПФ), так как этот вид обработки весьма характерен для многих применений.

Обмен 8-разрядными командами и данными между микропроцессором и внешними устройствами производится по 8-разрядной внешней шине данных DO — D7 через буферный регистр данных, который может находиться в трех состояниях — О, 1 и с высоким выходным сопротивлением, т.е. когда он отключается от внешней шины данных.

Снаружи процессор представляет собой 32-битовое устройство. Внешняя шина данных к памяти является 64-битовой, удваивая количество данных, передаваемых в течение одного шинного цикла.

Обмен кодами между памятью команд, памятью данных, периферийными устройствами и МП осуществляется через двунаправленный буфер шины данных. Последний изолирует внешнюю шину данных от внутренней. Это позволяет упростить подключение к одной шине нескольких устройств.

Обзор шин пк.

Все компоненты ПК объединены между

собой проводниками (кабелями) позволяющими

обмениваться данными, адресной

информацией, управлять режимами работы,

подключать питание и т.д.

Группы проводников, объединённые по

определённым признакам носят название

шин или магистралей.

В архитектуре ПК выделяют системные

шины (шины расширения — Expansion Bus) и

локальные шины. Основной обязанностью

системной шины является передача

информации между базовым МП и остальными

электронными компонентами компьютера.

Локальные шины вводятся для повышения

производительности ПК при работе с

устройствами, требующими передачи

больших объёмов информации (например,

накопителей, видеоадаптеров). Локальные

шины связывают между собой процессор

непосредственно с контроллерами

периферийных устройств.

Как следует из названия системные шины

(шины расширения) предназначены для

подключения различных адаптеров

периферийных устройств, расширяющих

возможности компьютера.

Интерфейсы шин начали свою историю с

8-битной шины ISA. Открытость этой шины

обеспечила появление широкого спектра

плат расширения, позволяющих использовать

PC в различных случаях, вплоть до применения

в качестве управляющего компьютера в

различных системах автоматизации.

С появлением АТ-286 шина ISA была

модифицирована, что позволило повысить

её производительность. Шина EISA явилась

откликом на потребность в

высокопроизводительном обмене для

серверов. Это довольно дорогая шина и

распространена не так широко. В шину

EISA можно установить и ISA – адаптеры.

Шина МСА, выдвинутая фирмой IBM как

прогрессивная альтернатива ISA, не была

поддержана производителями блоков PC,

так её спецификация не была открытой.

В результате она практически отмерла

вместе с семейством ПК IBM PS/2.

C появлением МП i486 появилась потребность

в повышении производительности

вычислительной системы, т.о. родилась

локальная шина VLB. Принципиальная

привязка к шине процессора 486 не обеспечила

ей долгого существования — пришла пора

Pentium.

С процессорами 486 появилась и другая

скоростная шина PCI. Она является новым

этажом в архитектуре PC , к которому

подключается шина типа ISA/EISA.

Шина PCI является в настоящее время

стандартной для ПК и используется с

процессорами 4,5 и 6 поколений.

Развитием шины PCI, нацеленным на дальнейшее

повышение производительности обмена,

является порт AGP, специально предназначенный

для подключения мощных графических

адаптеров.

Местоположение шин в архитектуре

современных ПК иллюстрирует рис.26.1.

Рис.26.1.

Когда ведущие устройства не могут уживаться вместе

Часть того, что делает I2C настолько универсальной, – это поддержка нескольких ведущих устройств. Но, как показывает предыдущий раздел, ведущие устройства не всегда хорошо работают вместе. Логика I2C устройства должна быть в состоянии определить, свободна ли шина; если шину занял другой мастер, то устройство до запуска своей собственной транзакции ждет, пока не завершится текущая транзакция. Но что происходит, когда два (или более) мастера пытаются инициировать транзакцию одновременно? I2C обеспечивает эффективное и удивительно простое решение этой неприятной, если бы она случилась, проблемы. Этот процесс называется «арбитраж», и он полагается на гибкость схемы шины I2C с открытым стоком: если один мастер пытается привести сигнал к логической единице, а другой мастер пытаются привести сигнал к логическому нулю, то «выиграет» мастер с логическим нулем, и, кроме того, «проигравший» может обнаружить, что фактическое состояние на выходе отличается от состояния, которое он хотел установить:

Арбитраж на шине I2C

Арбитраж на шине I2C

Эта схема показывает основу арбитража I2C; процесс происходит следующим образом:

- Оба мастера генерируют стартовые биты и осуществляют свои передачи.

- Если мастера выбирают на линии одни и те же логические уровни, ничего не происходит.

- Как только мастера пытаются установить на линии разные логические уровни, мастер, установивший на линии логический ноль, объявляется победителем; а проигравший обнаруживает несоответствие логических уровней и отказывается от своей передачи.

Потратьте минутку, чтобы оценить простоту и эффективность этого механизма:

- Победитель продолжает свою передачу без перерыва – нет поврежденных данных, нет конфликта устройств, нет необходимости в перезапуске транзакции.

- Теоретически проигравший мог контролировать адрес ведомого устройства в ходе процесса арбитража и фактически принимать правильные данные, если так оказалось, что он и является этим ведомым устройством.

- Если конкурирующие мастера запрашивают данные от одного и того же ведомого устройства, процесс арбитража не требует необязательного прерывания транзакции – не будет обнаружено ошибки, и ведомое устройство выведет свои данные на шину, чтобы их могли получить несколько мастеров.

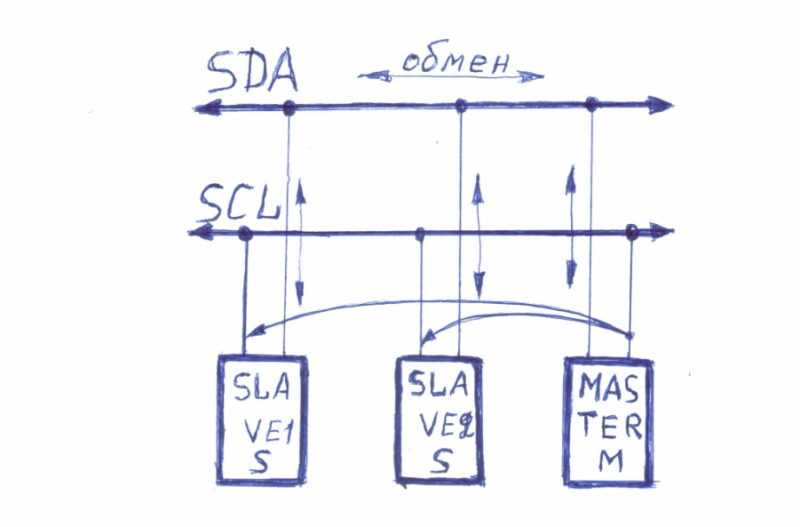

Шина I2C

I2C (Inter Integrated Circuit) – простая двунаправленная шина обмена данных. Имеет в своей конструкции два провода. Разработана компанией Philips в 80-х годах. Широко применяется в интегральной схемотехнике. Шина сконструирована как простая сигнальная.

Провода имеют следующие названия:

- SDA (Serial Data) – шина данных

- SCL – (Serial Clock) – тактовая шина

Структурная схема шины I2C

Устройства подключаемые к шине, присоединяются к каждому из проводов. Основным является MASTER (ведущее устройство). Он формирует тактовые сигналы, начало и конец передачи на шине данных. Таким образом импульсы исходят от него, а данные могут проходить в обе стороны.

Данные могут формироваться как MASTER, так и другими “подчиненными” устройствами:

- измерители

- АЦП

- ЖКИ

- память

- электронные датчики

- др.

Все указанные в списке устройства подключаются к шине параллельно. На одной электронной плате, подчиненных устройств может быть большое количество.

Стандарт шины имеет наличие адреса. Выделяется 7 бит, то есть два в седьмой степени, и означает количество устройств порядка 100.

Частоты на шине f = 100 – 10 кбит/с. Поэтому она является низкоскоростной. Общая емкость по шине не должно превышать 400 пФ (которое складывается из всех подключаемых к ней устройств). Питание на шине может быть:

- 3,3 V

- 5,0 V

Сигнальные линии подтянуты к питающему устройству через резисторы, сопротивление которых от 5 до 10 кОм

Это важно, так как благодаря этому изменяется паразитная емкость, что в свою очередь влияет на количество SLAVE и скорость передачи информации. Длина шины может достигать нескольких метров.

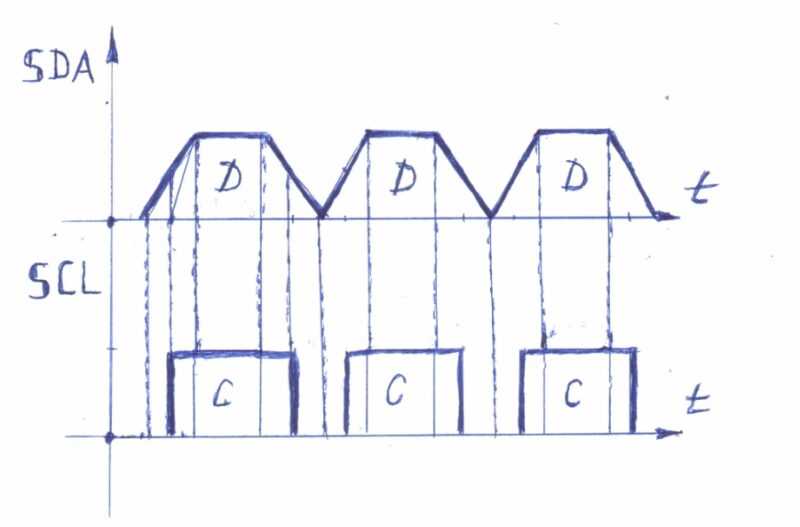

Алгоритм передачи данных:

- Данные могут меняться, когда на шине SCL присутствует 0 (логический уровень). Если на SCL присутствует 1 (логический уровень), данные меняться не могут. В данном случае возникают две ситуации, когда на шине SCL происходит переход:

- из 1 в 0

- из 0 в 1

Это означает, что MASTER хочет обменяться информацией с “подчиненными” устройствами и подает команду “ВНИМАНИЕ”. При переходе:

- из 1 в 0 – стартовая ситуация

- из 0 в 1 – стоповая ситуация

Важно помнить, что сигнал SCL может формировать только MASTER

- Вся передача передается байтами. Байты передаются побитно, начиная со старшего бита. В ответ на каждый полученный байт, приемник выставляет либо подтверждение, либо отказ.

Преимущества шины I2C:

- простота конструкции

- возможность подключения подчиненных SLAVE без отключения питания

Недостатки шины I2C:

ограничение по емкости

Организация передачи и приема данных по шине I2C

Типовая транзакция

Устройства, связанные через I2C, должны поддерживать определенную последовательность событий. Каждое событие соответствует определенному способу управления линиями тактовой синхронизации (SCK) и данных (SDA); как обсуждалось в статьях, приведенных в списке «Вспомогательная информация», эти два сигнала являются единственным средством, с помощью которого устройства на шине могут обмениваться информацией. Мы будем рассматривать одну информационную последовательность как «транзакцию»; это слово более уместно, чем «передача», поскольку каждая транзакция включает в себя как переданные данные, так и полученные данные, хотя в некоторых случаях единственными полученными данными являются бит подтверждения (ACK) или не-подтверждения (NACK), детектируемые ведущим устройством. Следующая временная диаграмма показывает типовую транзакцию I2C.

Временная диаграмма типовой транзакции I2C

Временная диаграмма типовой транзакции I2C

Обратите внимание на следующее:

- Пунктирная линия, соответствующая длительности логической единицы в тактовом сигнале, напоминает нам, что логическая единица (и для SCL, и для SDA) является «рецессивным» состоянием – другими словам, сигнал доходит до высокого логического уровня с помощью подтягивающего резистора. «Доминантное» состояние – это логический ноль, потому что сигнал будет на низком логическом уровне только тогда, когда устройство действительно приводит его к состоянию логического нуля.

- Транзакция начинается со «стартового бита». Каждая I2C транзакция должна начинаться со стартового бита, который определятся как спадающий фронт на линии SDA, в то время как линия SCL находится в состоянии логической единицы.

- Транзакция заканчивается «стоповым битом», определяемым как нарастающий фронт на линии SDA, в то время как линия SCL находится в состоянии логической единицы. Транзакции I2C должны заканчиваться стоповым битом; однако, как будет рассказано позже, на шине могут появиться несколько стартовых битов до того, как будет сгенерирован стоповый бит.

- Данные действительны, когда на линии синхронизации установлена логическая единица, и изменяют состояние, когда на линии синхронизации установлен логический ноль; цифровые системы связи обычно ориентируются на изменения состояния на линиях, поэтому на практике данные считываются по нарастающему фрону на линии синхронизации и обновляются по спадающему фронту на линии синхронизации.

- Обмен информацией происходит по одному байту за раз, начиная со старшего значащего бита; и за каждым байтом следует ACK или NACK.

- Вы можете ожидать, что ACK будет обозначаться логической единицей, а NACK – логическим нулем, но в данном случае это не так. ACK соответствует логическому нулю, а NACK – логической единице. Это необходимо, потому что логическая единица является рецессивным состоянием – если ведомое устройство не работает, то сигнал, соответственно, будет поднят до NACK. Аналогично, ACK (указывается доминантным логическим нулем) может быть передан только в том случае, если устройство работает и готово продолжить транзакцию.

Следующий список описывает последовательность событий в вышеуказанной транзакции:

- Ведущее устройство генерирует стартовый бит, чтобы начать транзакцию.

- Ведущее устройство передает 7-битный адрес, соответствующий ведомому устройству, с которым оно хочет установить соединение.

- Последним битом в первом однобайтовом сегменте является индикатор чтения/записи. Мастер устанавливает этот бит в логическую единицу, если он хочет считывать данные с ведомого устройства, или в логический ноль, если хочет записать данные в ведомое устройство.

- Следующий байт – это первый байт данных. Он приходит либо от ведущего, либо от ведомого устройства, в зависимости от состояния бита чтения/записи. Как обычно, у нас есть 8 бит данных, начинающихся со старшего значащего бита.

- За байтом данных следует ACK или NACK, сгенерированный ведущим устройством, если это транзакция чтения, или ведомым устройством, если это транзакция записи. ACK и NACK могут означать разные вещи в зависимости от прошивки или низкоуровневой аппаратной схемы взаимодействующих устройств. Например, мастер может использовать NACK, чтобы сказать: «это последний байт данных», или если ведомое устройство знает, сколько данных должно быть отправлено, оно может использовать ACK для подтверждения того, что данные были успешно получены.

- Транзакция завершается стоповым битом, сгенерированным ведущим устройством.

Зачем разделять двунаправленную шину?

Спецификация шины I2C [] содержит пример эталонной схемы, позволяющей разделять ее на входную и выходную пары. Такая конфигурация может потребоваться по нескольким причинам. Прежде всего, разделение шины используется для оптической изоляции ведущего устройства от ведомых при повышенных требованиях к безопасности, в случае зашумленности линий передачи или при невозможности обеспечить надежное заземление (Рисунок 1). Кроме того, сигналы разделенной шины можно усиливать (Рисунок 2), а, заменив усилитель схемой преобразователя интерфейсов, можно сменить среду передачи информации. Это позволяет увеличить рабочую длину шины и улучшить ее характеристики за счет снижения емкости. По мере снижения емкости линий доминирующее влияние на постоянную времени шины начинают оказывать подтягивающие резисторы.

|

|

| Рисунок 1. | Изоляция двунаправленной шины. |

Для разработчиков контроллеров двунаправленных шин разделение шины может использоваться в целях отладки. Обычно отладка двунаправленных протоколов представляет собой непростую задачу, поскольку вполне вероятна ситуация, при которой работающий неправильно контроллер выставляет на шине «0» в то же время, когда другой контроллер пытается установить контроль над шиной. Это сделает идентификацию передающего устройства на шине невозможной без информации о внутренних состояниях контроллеров всех устройств. Однако контроль линий /gateB1 и /gateA2 (Рисунок 2) позволяет идентифицировать оба передающих устройства и выявлять любые одновременные обращения с использованием лишь стандартного лабораторного оборудования и обычных технологий отладки.

|

|

| Рисунок 2. | Повторитель двунаправленной шины. |

Наконец, возможно использование технологии разделения шины для подключения устройства, поддерживающего интерфейс I2C, к другому устройству, не имеющему контроллера I2C. В этом случае разделенная шина может быть подключена к портам вывода/вывода общего назначения другого устройства (Рисунок 3).

|

|

| Рисунок 3. | Разделенная шина, подключенная к порту ввода/вывода общего назначения. |

Опубликовано немало схем, позволяющих разделять двунаправленные шины. К сожалению, примеры решений, демонстрирующих разделение шин, требуют разработки специальных схем для каждого приложения (как следует из публикаций) или внешней управляющей логики (как показано в описании стандарта I2C), использующей проходные логические вентили для того, чтобы в процессе обмена не образовывались замкнутые контуры, приводящие к «защелкиванию». Условия для защелкивания, очевидным образом, существуют в схеме на Рисунке 2, где узел IOA, выставив на шине «0», через /gateB1 открывает транзистор Q1, в результате чего потенциал узла IOB опускается в «0», что, в свою очередь, открывает Q2 высоким уровнем на /gateA2, опуская вниз потенциал IOA.

|

|

| Рисунок 4. | Схема двухстороннего арбитража. |

Представленный в этой статье двухсторонний арбитр может разделять шину на передающую и приемную пары, и сконструирован универсальным, что позволяет использовать его в любых приложениях с разделенной шиной. Кроме того, он не требует внешней управляющей логики – управление осуществляется исключительно на основании состояния шины данных (Рисунок 4).

История

Разработана фирмой Philips Semiconductors в начале 1980-х как простая 8-битная шина внутренней связи для создания управляющей электроники. Была рассчитана на частоту 100 кГц.

Стандартизована в 1992 году, в первой версии к стандартному режиму 100 кбит/с добавлен скоростной режим 400 кбит/с (Fast-mode, Fm); за счёт 10-битной адресации становится возможным подключение на одну шину более 1000 устройств, количество которых ограничивается максимально допустимой ёмкостью шины — 400 пФ.

В стандарте версии 2.0 (1998 год) представлены высокоскоростной режим работы 3,4 Мбит/с (High-speed mode, Hs) и требования пониженного энергопотребления. Незначительно доработан в версии 2.1 (2000 год).

В версии 3 (2007 год) добавлен режим 1 Мбит/с (Fast-mode plus, Fm+) и механизм идентификации устройств (ID).

В версии 4 (2012 год) появился однонаправленный режим 5 Мбит/с (Ultra Fast-mode, UFm) с использованием двухтактной логики без подтягивающих резисторов, добавлена таблица предустановленных идентификаторов.

В версии 5 (2012 год) исправлены ошибки.

В версии 6 (2014 год) пересчитаны графики, определяющие величину подтягивающих резисторов в зависимости от ёмкости шины и рабочего напряжения.

Двунаправленная шина

Двунаправленная шина ( bidirectional bus) — шина, по которой передача данных возможна в обоих направлениях.

Шина данных — двунаправленная шина , по которой данные могут на правляться либо в микропроцессор, либо нз него ( на рнс. По такой шине данные невозможно одновременно передавать в обоих направлениях. Эти процедуры разнесены во времени в результате применения временного мультиплексирования.

Устройство 8251 имеет 8-разрядную двунаправленную шину , с помощью которой можно получать данные из процессора и передавать их в процессор. В дополнение к этому процессор может считывать по этой шине информацию о состоянии устройства 8251, а также программировать режим работы устройства.

Третий режим называется стробируемым ВВ с двунаправленной шиной .

Системная магистраль ( табл. 3.4) использует двунаправленные шины адреса изданных. Часть контактов соединителя ( в таблице отсутствуют) зарезервирована, для расширения шин данных до 32 разрядов и шин адреса до 24 разрядов, часть линий — для дополнительных управляющих сигналов.

Буферная схема данных ( БД) представляет собой 8-разрядную двунаправленную шину с тремя состояниями, соединяющую микросхему с системной шиной данных.

Блок управления шинами осуществляет двустороннюю связь между двунаправленными шинами IB и ФВ и внутренними регистрами микросхемы.

Для уменьшения числа шин в этом интерфейсе осуществляется временное разделение двунаправленных шин , используемых как для обмена информацией, так и для адресации. Упорядочение обмена, идентификация сигналов, синхронизация обеспечиваются группой управляющих шин. Управление прерываниями осуществляется сигналами запроса прерывания и разрешением — прерына-ния, последовательно проходящими через все источники прерываний в системе. По отдельной шине передается сигнал принадлежност i данного адреса группе адресов внешних устройств. Управление общим сбросом системы при отключении источника питания осуществляется по трем шинам. Три другие шины используются для сигнализации о переходе в режим работы с пульта, о работе в реальном масштабе времени и о перезаписи микрокодов в памяти. Специальные шины служат для управления запросами прямого доступа в память.

На рисунке в качестве примера показано, что в процессоре к двунаправленной шине присоединены как входные усилители, принимающие сигналы из интерфейса, так и выходные формирователи, посылающие сигналы в другие устройства. Подобное имеет место и в ПУ.

Особенностью функционального построения БИС является использование мультиплексорных и регистровых схем, а также двунаправленных шин входа / выхода, придающих большую гибкость системе.

На рис. 3.18 представлена структура ЦПУ, построенного на компонентах семейства SN — 74AS88XX и содержащего три двунаправленные шины ввода-вывода ( каждая из которых состоит из 32 линий данных и четырех линий контроля четности) и шину управления, служащую для пересылки микрокоманд из устройства, управляющего последовательностью их выполнения, в другие процессорные элементы для исполнения.

Двунаправленные усилители записи / считывания каналов А и В обеспечивают прием входной информации з режиме записи с 4-разрядной двунаправленной шины DA или DB и выдачу информации на эти же шины в режиме считывания.

Двунаправленные усилители записи / считывания каналов А и В обеспечивают прием входной информации в режиме записи с 4-разрядной двунаправленной шины DA или DB и выдачу информации на эти же шины в режиме считывания. Усилители записи / считывания каналов А и В имеют на выходе состояние Выключено, установка которого осуществляется подачей на вход RA или RB Считывание напряжения высокого уровня.

Сигналы на шинах ввода / вывода SYNC, DIN, DOUT, WTBT, PRLY обеспечивают управление передачей по 16-разрядной двунаправленной шине ОАО-DA15 команд , адресов, данных и векторов.

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле

2 Системныеблоки корпуса персональных компьютеров

Системные

блоки IBM РС выполняются в различных

геометрических вариантах. Так по форме,

расположению внутренних узлов, рабочему

положению и размерам, обычно, выделяют

корпуса с вертикальным и горизонтальным

пространственным расположением элементов.

Корпуса с

горизонтальным расположением делят на типы:

нормальный (normal), малый (baby)

и сверх малый (slim)

Корпуса

с вертикальным расположением называют

типом башня (tower) и делят на виды: 1 – малый (mini

tower), 2 – средний (midi tower) и 3 – большой (big tower).

Как правило, корпуса такого исполнения

отличаются друг от друга видом передней

панели и общей полезной высотой, в то время

как, их ширина, длинна и глубина различаются

незначительно. На передней панели

системного блока располагаются некоторые

элементы управления, а именно: тумблер-выключатель

напряжения питания сети (Power), кнопка сброса

– перезагрузки (Reset), кнопка включения/выключения

режима турбирования (Turbo), индикаторы этих

режимов, индикатор обращения к жесткому

диску, передние панели дисковых и ленточных

устройств — накопителей информации со

сменными носителями и другие комплектующие

элементы и части устройств, требующие

простого и частого доступа при

использовании.

Внутри

Внутри

системного блока размещаются основные

внутренние компоненты персонального

компьютера: материнская плата – 3, платы

адаптеров, интерфейсов, контроллеров

устройств, карт, расширений и их разъемы –

10, дисковые накопители – 8 и 13, блок питания

– 6, соединительные шлейфы, шнуры и кабели –

4, 7, вентилятор системы охлаждения

внутренних элементов – 1, вентилятор и

радиатор системы охлаждения центрального

процессора – 2, слоты системной шины – 9,

отверстие разъема клавиатуры – 11 и входной

и выходной разъемы подключения питания – 12

и т.д.. Так как многие компоненты могут быть

интегрированы на материнской плате, то не

все они могут быть представлены как

отдельные комплектующие элементы. Задняя

панель, как правило, содержит панели плат

расширений с разъемами, заглушки разъемов,

вентиляционное отверстие вентилятора

блока питания – 5 и др.

Корпус

может быть выполнен из металла, пластика и

комбинации того и другого. Как правило, все

комплектующие элементы, расположенные

внутри системного блока, крепятся изнутри к

металлической раме – 3, состоящей из днища

– 8, задней панели – 3 и передней панели – 7,

на которую затем надевается кожух – 2. В

передней панели имеется одно или несколько

окон – 1, предназначенных для вывода на

лицевую – переднюю часть управляющих

панелей устройств, требующих постоянного

доступа во время эксплуатации (магнитные,

оптические, магнитооптические дисководы,

ленточные накопители и др.). Задняя панель,

также, имеет отверстия и окна для вывода на

заднюю часть системы охлаждения блока

питания – 4, разъемов интерфейсов

периферийных устройств – 5, заглушек плат

интерфейсных карт – 6.

Шина USB

Шина USB (Universal Serial Bus) наиболее распространенный способ подключения внешних устройств к материнской плате телевизора, ноутбука и других устройств. Данная шина разработана в 1996 году, широкое применение получила начиная с 2000 года, с появлением первой Flash.

На данный момент шина имеет три стандарта отличающихся скоростью передачи данных:

- USB 1 примерно 12 МБит/с

- USB 2 примерно 450 МБит/с

- USB 3 примерно 5 ГБит/с

Шина USB является асимметричной и работает по типу MASTER-SLAVE. Драйвера у шины разные. Один из них Downstream – управляет поведением шины данных от устройства

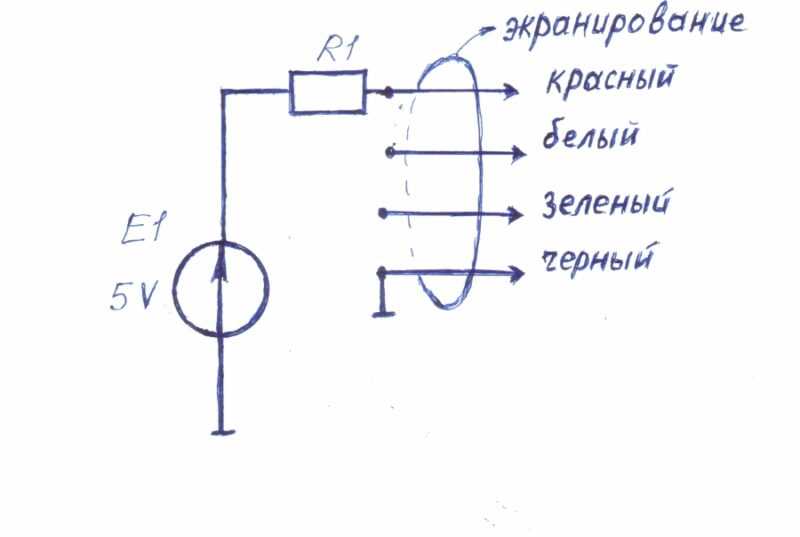

Шина устройства представляет из себя четыре проводника, являющихся сигнальными проводами обернутыми в защитную землю. Провода идут со стандартной цветовой маркировкой: красный, белый, зеленый, черный. По красному и черному проводу передается напряжение питания – 5V. И рассчитано на ток в 100 мА для одного устройства. К одному устройству можно подключать до 5 внешних устройств, соответственно до 500 мА.

Схема подключения устройства имеет следующий вид:

Схема подключения

По белому и зеленому проводу осуществляется дифференциальная передача сигналов. Передача управляется при помощи передатчиков управлений кодером, по соответствующим сигналам.

Второй драйвер – Upstream. Расположен на стороне приемника, управляется кодером для передачи данных, аналогично как Downstream.

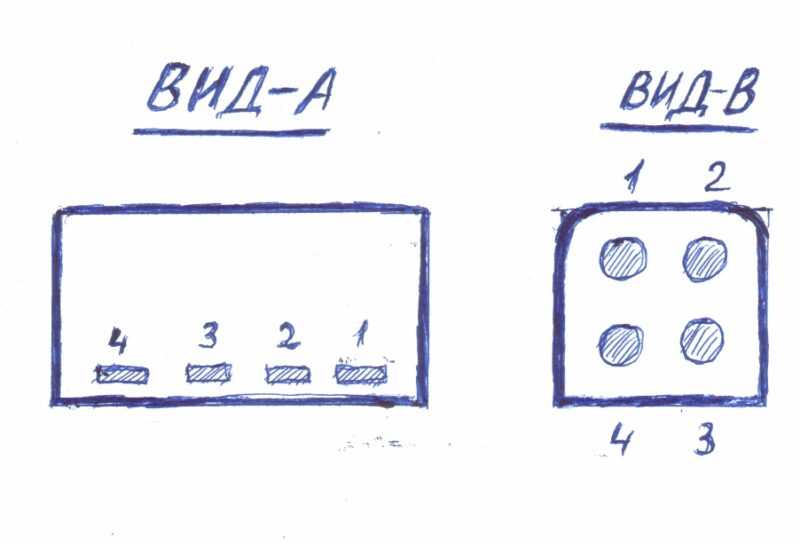

Разъемы подключения шин имеют следующий вид:

Схема подключения USB портов